A3V28S40JTP Zentel 128M Single Data Rate Synchronous DRAM IC

Features

- Single 3.3V ±0.3V power supply

- Maximum clock frequency:

- 60:166MHz<3-3-3>/-70:143MHz<3-3-3>/-75:133MHz<3-3-3>

- Fully synchronous operation referenced to clock rising edge

- 4-bank operation controlled by BA0, BA1 (Bank Address)

- /CAS latency- 2/3 (programmable)

- Burst length- 1/2/4/8/FP (programmable)

- Burst type- Sequential and interleave burst (programmable)

- Byte Control- LDQM and UDQM (A3V28S40JTP)

- Random column access

- Auto precharge / All bank precharge controlled by A10

- Support concurrent auto-precharge

- Auto and self refresh

- 4096 refresh cycles /64ms

- Temperature range: -40℃ to +85℃

- LVTTL Interface

- Package

400-mil, 54-pin Thin Small Outline (TSOP II) with 0.8mm lead pitch

A3V28S40JTP Zentel 128M Single Data Rate Synchronous DRAM IC Photo:

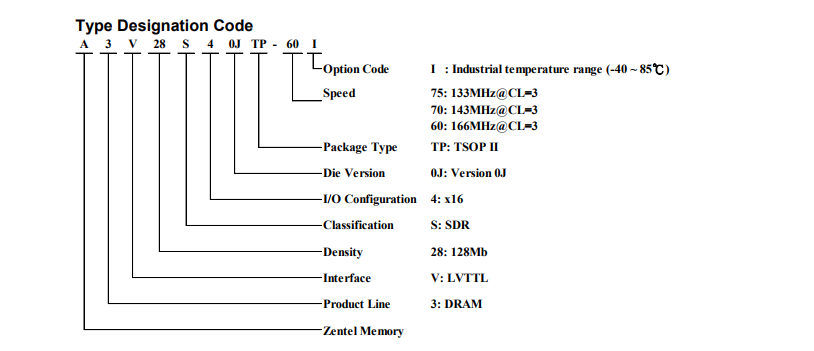

A3V28S40JTP Zentel 128M Single Data Rate Synchronous DRAM IC Marking information:

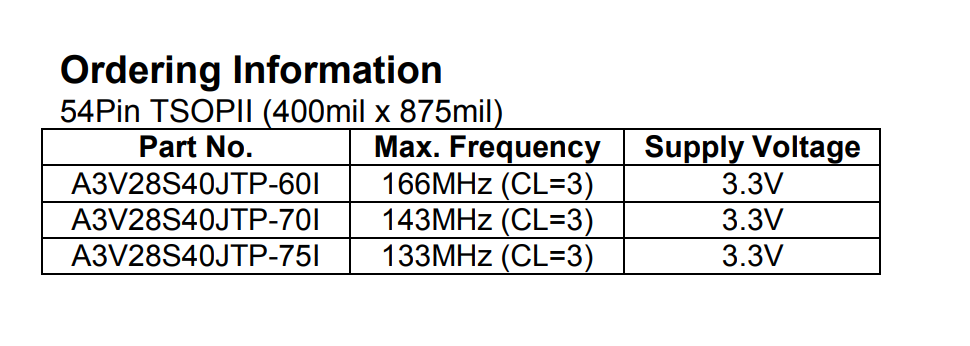

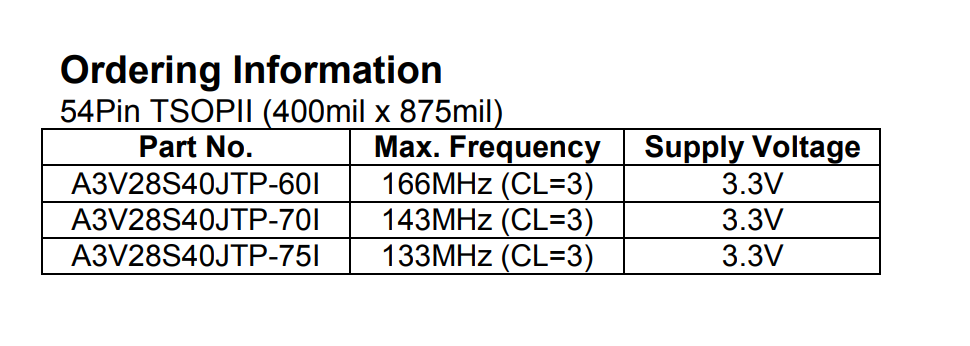

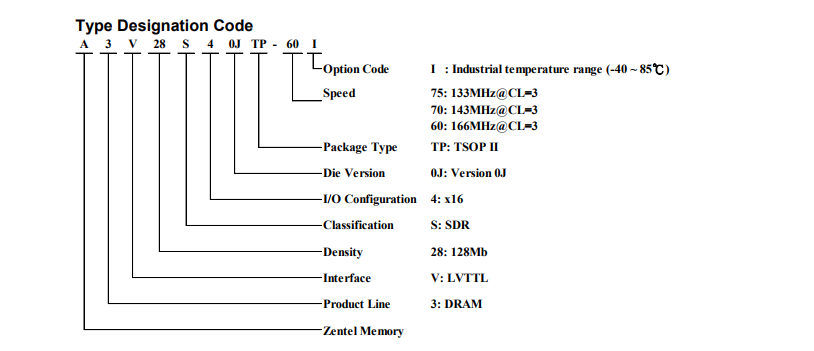

A3V28S40JTP Zentel 128M Single Data Rate Synchronous DRAM IC ordering information :