A3R56E40ABF ZENTEL 256Mb DDR2 SDRAM IC

Specifications:

• Density: 256M bits

• Organization

⎯ 4M words × 16 bits × 4 banks (A3R56E40ABF)

• Package

⎯ 84-ball FBGA(μBGA) (A3R56E40ABF)

⎯ Lead-free (RoHS compliant)

• Power supply: VDD, VDDQ = 1.8V ± 0.1V

• Data rate: 1066Mbps/800Mbps(max.)

• 1KB page size (A3R56E40ABF)

⎯ Row address: A0 to A12

⎯ Column address: A0 to A8

• Four internal banks for concurrent operation

• Interface: SSTL_18

• Burst lengths (BL): 4, 8

• Burst type (BT):

⎯ Sequential (4, 8)

⎯ Interleave (4, 8)

• /CAS Latency (CL): 3, 4, 5, 6, 7

• Precharge: auto precharge option for each burst

access

• Driver strength: normal/weak

• Refresh: auto-refresh, self-refresh

• Refresh cycles: 8192 cycles/64ms

⎯ Average refresh period

7.8μs at 0°C ≤ TC ≤ +85°C

3.9μs at +85°C < TC ≤ +95°C

• Operating case temperature range

⎯ TC = 0°C to +95°C

Features:

• Double-data-rate architecture; two data transfers per clock cycle

• The high-speed data transfer is realized by the 4 bits prefetch pipelined architecture

• Bi-directional differential data strobe (DQS and /DQS) is transmitted/received with data for capturing data at the receiver

• DQS is edge-aligned with data for READs; centeraligned with data for WRITEs

• Differential clock inputs (CK and /CK)

• DLL aligns DQ and DQS transitions with CK transitions

• Commands entered on each positive CK edge; data and data mask referenced to both edges of DQS

• Data mask (DM) for write data

• Posted /CAS by programmable additive latency for better command and data bus efficiency

• On-Die-Termination for better signal quality

• /DQS can be disabled for single-ended Data Strobe operation

• Off-Chip Driver (OCD) impedance adjustment is not supported

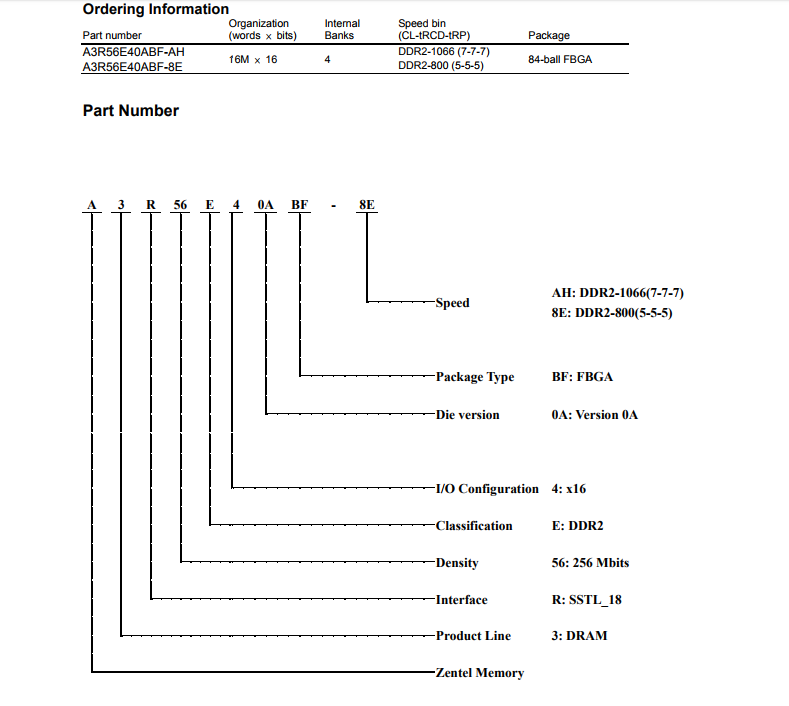

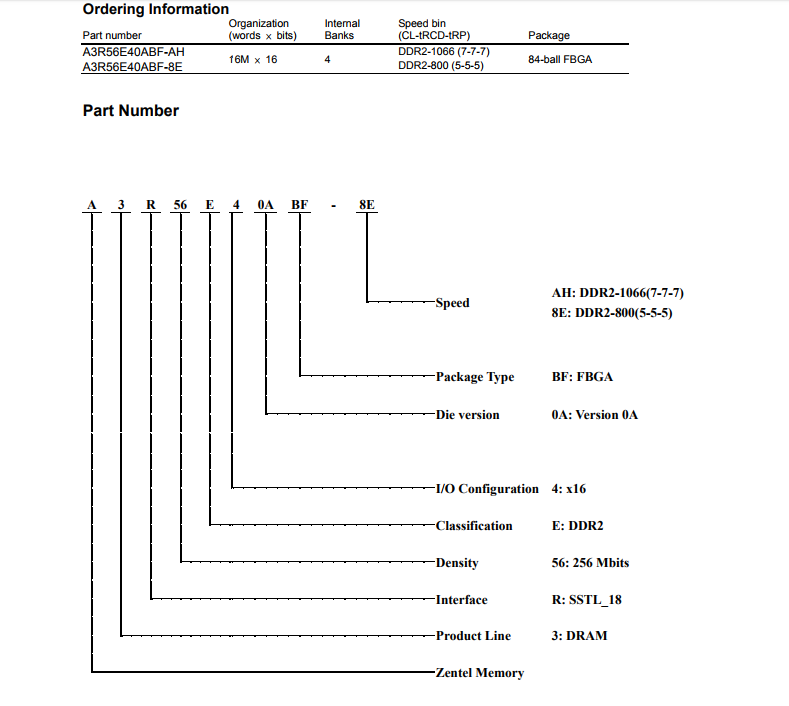

A3R56E40ABF ZENTEL 256Mb DDR2 SDRAM IC Ordering information: